26 اکتبر 2023 -توسط آندریاس اشمیتز، دانشگاه فنی مونیخ

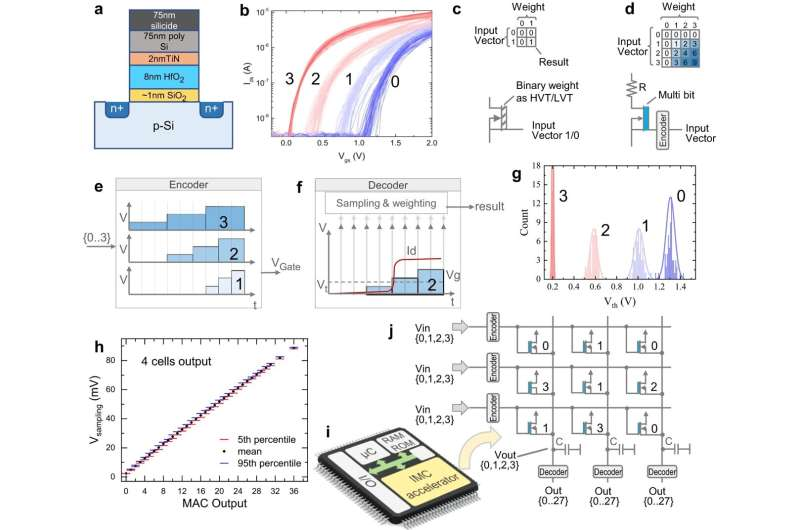

مروری بر ماکرو IMC پیشنهادی برای عملیات MAC. a مجموعه مواد FeFETs. b

FeFET چند بیتی را می توان در حالت های مختلف برای ذخیره وزن سیناپس برنامه ریزی کرد. c کارهای قبلی 7، 8، 11 فقط عملیات باینری AND یا XNOR را برای محاسبه عملیات ضرب تک بیتی در نظر می گرفتند. d عملیات ضرب 2 بیتی پیشنهادی ما با رمزگذاری ورودی و ذخیره سازی 2 بیتی نشان داده شده است. خروجی مربوطه در موارد مختلف زمانی فعال می شود. e یک رمزگذار ولتاژ گیت را بسته به مقدار ورودی که بین سه سطح در زمانهای مختلف تغییر میکند، فراهم میکند. f خروجی ضرب حالت ورودی و ذخیره شده در سلول بستگی به زمانی دارد که یک سلول فعال می شود که با استفاده از رمزگشا جمع آوری و نمونه برداری می شود. g توزیع V ام چهار حالت برای منحنی های Ids–Vgs نشان داده شده است. h بسته به زمان فعالسازی و تعداد سلولهای فعال شده در یک زمان معین، ولتاژ در خازن متصل به ستونی از سلولها انباشته میشود که به صورت خطی با خروجی MAC مطابقت دارد و کمترین تأثیر را بر تغییرات دستگاه زیرین دارد. شتابدهندههای IMC عملیات MAC را برای بارهای کاری هوش مصنوعی تسهیل میکنند، جایی که میتوان از طرح پیشنهادی ما استفاده کرد. j عملیات MAC مربوطه در crossbar انجام می شود و خروجی را در ولتاژ خازن جمع می کند. اعتبار: Nature Communications (2023). DOI: 10.1038/s41467-023-42110-y

حسام امروش معماری آماده هوش مصنوعی را توسعه داده است که دو برابر قدرتمندتر از رویکردهای محاسباتی در حافظه قابل مقایسه است. همانطور که در مجله Nature Communications گزارش شده است، استاد دانشگاه فنی مونیخ (TUM) یک الگوی محاسباتی جدید را با استفاده از مدارهای ویژه ای به نام ترانزیستورهای اثر میدان فروالکتریک (FeFETs) اعمال می کند. ظرف چند سال، این می تواند برای هوش مصنوعی مولد، الگوریتم های یادگیری عمیق و برنامه های روباتیک مفید باشد.

ایده اصلی ساده است: برخلاف تراشههای قبلی، که فقط محاسبات روی ترانزیستورها انجام میشد، اکنون محل ذخیرهسازی دادهها نیز هستند. که باعث صرفه جویی در زمان و انرژی می شود. حسام امروش، استاد طراحی پردازنده های هوش مصنوعی در دانشگاه فنی مونیخ (TUM) می گوید: «در نتیجه، عملکرد تراشه ها نیز افزایش می یابد. ترانزیستورهایی که او محاسبات را روی آنها انجام می دهد و داده ها را ذخیره می کند، تنها 28 نانومتر اندازه گیری می کنند که میلیون ها عدد از آنها روی هر یک از تراشه های هوش مصنوعی جدید قرار می گیرند.

تراشه های آینده باید سریعتر و کارآمدتر از تراشه های قبلی باشند. در نتیجه، آنها نمی توانند به سرعت گرم شوند. این امر برای پشتیبانی از چنین برنامه هایی مانند محاسبات بلادرنگ در هنگام پرواز، ضروری است. پروفسور توضیح میدهد: «وظایفی مانند این برای رایانه بسیار پیچیده و انرژیزا هستند.

این الزامات کلیدی برای یک تراشه به صورت ریاضی با پارامتر TOPS/W خلاصه میشود: «عملیات ترا بر ثانیه بر وات». این می تواند به عنوان ارز برای تراشه های آینده دیده شود. سوال این است که یک پردازنده با یک وات (W) توان، چند تریلیون عملیات (TOP) در هر ثانیه (S) می تواند انجام دهد.

تراشه جدید هوش مصنوعی که با همکاری Bosch و Fraunhofer IMPS توسعه یافته و در فرآیند تولید توسط شرکت آمریکایی GlobalFoundries پشتیبانی میشود، میتواند 885 TOPS/W را ارائه دهد. این باعث می شود تا دو برابر تراشه های هوش مصنوعی مشابه، از جمله تراشه MRAM سامسونگ، قدرتمندتر باشد. تراشههای CMOS که امروزه معمولاً مورد استفاده قرار میگیرند، در محدوده 10-20 TOPS/W کار میکنند.

محاسبات درون حافظه مانند مغز انسان کار می کند

محققان اصل معماری مدرن چیپ را از انسان قرض گرفتند. امروش با توضیح اینکه چگونه افراد می توانند روابط متقابل پیچیده را یاد بگیرند و به خاطر بیاورند، می گوید: «در مغز، نورون ها پردازش سیگنال ها را کنترل می کنند، در حالی که سیناپس ها می توانند این اطلاعات را به خاطر بسپارند. برای انجام این کار، تراشه از ترانزیستورهای “فروالکتریک” (FeFET) استفاده می کند.

اینها سوئیچ های الکترونیکی هستند که ویژگی های اضافی ویژه ای را در خود جای داده اند (معکوس شدن قطب ها هنگام اعمال ولتاژ) و می توانند اطلاعات را حتی در صورت قطع شدن منبع تغذیه ذخیره کنند. علاوه بر این، آنها ذخیره سازی و پردازش همزمان داده ها در ترانزیستورها را تضمین می کنند.

امروش میگوید: «اکنون میتوانیم چیپستهای بسیار کارآمدی بسازیم که میتوانند برای برنامههایی مانند یادگیری عمیق، هوش مصنوعی مولد یا روباتیک استفاده شوند، برای مثال جایی که دادهها باید در جایی که تولید میشوند پردازش شوند».

تراشه های آماده بازار نیاز به همکاری بین رشته ای دارند

هدف استفاده از این تراشه برای اجرای الگوریتمهای یادگیری عمیق، تشخیص اشیاء در فضا یا پردازش دادههای هواپیماهای بدون سرنشین در حال پرواز بدون تاخیر زمانی است. با این حال، پروفسور مؤسسه یکپارچه رباتیک و هوش ماشینی مونیخ (MIRMI) در TUM معتقد است که چند سالی طول می کشد تا این امر محقق شود.

او فکر میکند که در کوتاهترین زمان ممکن، سه تا پنج سال طول میکشد تا اولین تراشههای حافظه داخلی مناسب برای کار واقعی تولید شوند.

برنامه های ld در دسترس قرار می گیرند. یکی از دلایل این امر، از جمله، در الزامات امنیتی صنعت نهفته است. برای مثال، قبل از اینکه بتوان از این نوع فناوری در صنعت خودرو استفاده کرد، برای عملکرد قابل اعتماد کافی نیست. همچنین باید معیارهای خاص این بخش را برآورده کند.

کارشناس سخت افزار امروچ می گوید: «این دوباره اهمیت همکاری بین رشته ای با محققان رشته های مختلف مانند علوم کامپیوتر، انفورماتیک و مهندسی برق را نشان می دهد. او این را نقطه قوت ویژه میرمی می داند.