17 فوریه 2023 -توسط موسسه فناوری توکیو-اعتبار: فناوری توکیو

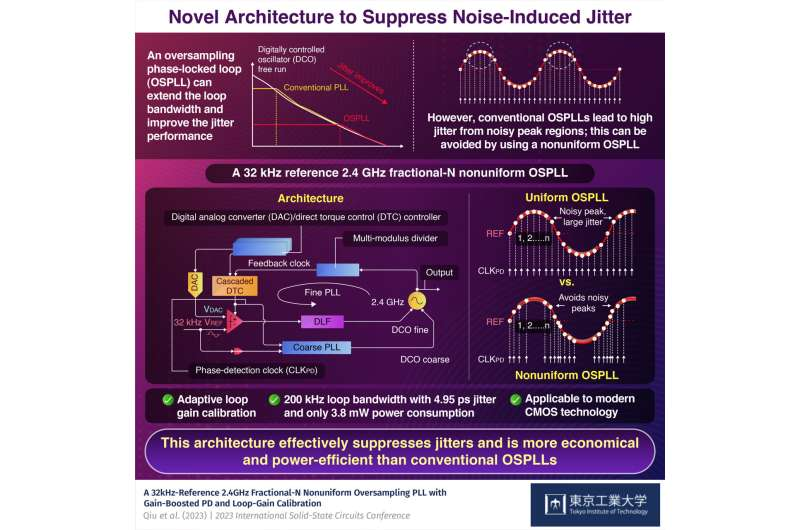

کارایی دستگاه های الکترونیکی مدرن اغلب به نویز سیگنال و لرزش آنها بستگی دارد. جیتر نوسان یا انحراف شکل موج سیگنال در یک سیگنال دیجیتال با فرکانس بالا است. روشهای مرسوم زیادی برای کاهش لرزش و افزایش ویژگیهای عملکرد یک دستگاه وجود دارد. یکی از روش های رایج استفاده از حلقه قفل شده فاز (OSPPL) نمونه برداری بیش از حد است. یک OSPLL می تواند پهنای باند حلقه را افزایش دهد و منجر به بهبود عملکرد جیتر شود.

در حال حاضر، در حالی که آنها مزایای بسیاری را ارائه می دهند، استفاده از OSPLL های معمولی منجر به لرزش زیاد از مناطق اوج پر سر و صدا می شود، زیرا مناطق اوج دارای گرادیان کوچکتری هستند. شیب مرجع آهسته یک سیگنال معمولی 32 کیلوهرتز، یک لرزش بزرگ ایجاد می کند و منجر به خطای زمانی نسبت داده شده بزرگتر می شود.

این نقطه ضعف تا کنون مانع استفاده گسترده از OSPLL ها شده است. اکنون تیمی از دانشمندان موسسه فناوری توکیو (Tokyo Tech) نشان دادهاند که چگونه میتوان با استفاده از OSPLL غیریکنواخت از این امر جلوگیری کرد.

پروفسور کنیچی اوکادا، که رهبری تیم تحقیقاتی را بر عهده داشت، توسعه را بیشتر توضیح میدهد: «معماری جدید نمونهبرداری بیش از حد، یک PLL کسری-N با سرعت کم، 2.4 گیگاهرتز با استفاده از مرجع 32 کیلوهرتز ارائه میکند. پهنای باند حلقه PLLهای معمولی از نظر تئوری محدود به 1/10 فرکانس مرجع، توسط تئوری پایداری گاردنر. این پهنای باند حلقه باریک باعث تخریب جیتر می شود. PLL نمونه برداری بیش از حد غیر یکنواخت ما می تواند پهنای باند حلقه را تا 60 برابر افزایش دهد و می تواند به طور موثری لرزش را سرکوب کند.”

معماری دستگاه که به تازگی طراحی شده است، امکان کالیبراسیون افزایش حلقه تطبیقی را فراهم می کند. با انجام خودکار کالیبراسیون بهره حلقه برای هر نقطه نمونه برداری، می توان لرزش را به حداقل رساند.

جونجون کیو از توکیو تک، نویسنده اصلی مطالعه آنها اضافه می کند.:

“عملکرد دستگاه ما با پهنای باند حلقه 200 کیلوهرتز با جیتر 4.95 ps برجسته می شود. در این پارامترها، دستگاه فقط 3.8 مگاوات انرژی مصرف می کند. علاوه بر این، می توان آن را با فناوری های CMOS ادغام کرد و آن را به چشم اندازی جذاب در حال رشد صنعت الکترونیک، برای همیشه تبدیل کرد. “

این معماری تغییر پارادایم همچنین به دلیل کاهش لرزش و سیگنال بالاتر و تمیزتر نسبت به OSPLL های معمولی مقرون به صرفه تر و کارآمدتر است.

این مقاله به عنوان بخشی از کنفرانس بین المللی مدارهای حالت جامد 2023 منتشر شده است.